19日目 ~DFF~

こんにちは!今日も引き続きデジタル回路の話題で更新していきます。

ALUは少し後回しにして、今回はDフリップ・フロップ回路(DFF)を紹介していきます。

DFF単体は、組み合わせ回路の出力を保存することのできる記憶素子です。

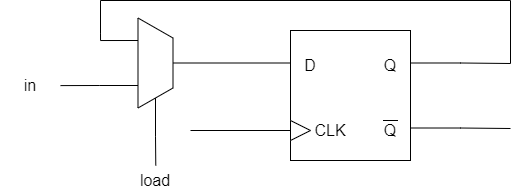

以下に示す図で、DFFがどんな記号か見てみます。

この図では、入力がD、出力がQとなっています。基本的に、CLKがL(0)からH(1)に立ち上がる時にDの信号値を受け取ります。そして、Qから出力するという回路なわけですが、このQの出力をまたDに繋いでやればデータが保持できるわけです。

しかし、このままでは入力を受け付けることができないため、

実際はマルチプレクサによりloadするかデータ保持かの条件分岐を行う必要があります。

よって、

と設計します。

これをVerilogHDLのコードで書き表すと以下のようになります。

module DFF (

input in, load, clk,

output out

);

reg d;

assign out = d;

always @(posedge clk) begin

if (load) begin

d = in;

end

end

endmodule

はてな記法にし忘れたため色分けできませんでしたが、短いコードなのでわかりやすいと思います。

このコード中ではマルチプレクサが出てきていませんが、ifの条件分岐がそれにあたります。クロックのposedge(positive edgeつまり、信号の立ち上がりのこと)中に、load信号がonであればDFFのにinのデータを取り込み、値を更新します。それ以外では、dの値をそのままoutへ垂れ流しています。また、dはレジスタとして宣言している為、この記述のみで値の保持ができます。

ALUより先に、記憶する回路に手を伸ばしてしまいました。しかし、着実にコンピュータの実装に近づいている気がします。

参考書籍